微型计算机的发展是以微处理器为标志

机器字长:计算机一次整数运算所能处理的二进制位数

摩尔定律揭示了信息技术进步的速度,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,整体性能也将提升一倍

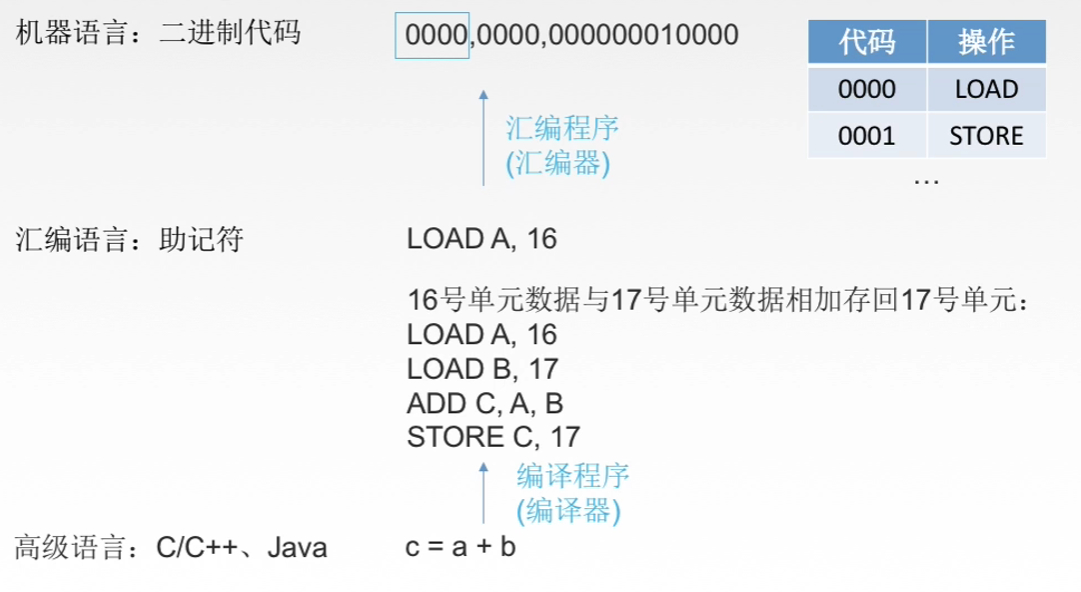

汇编、解释和编译是计算机程序语言处理的三种不同方式,它们的主要区别在于程序执行前如何将源代码转换成机器可执行的形式

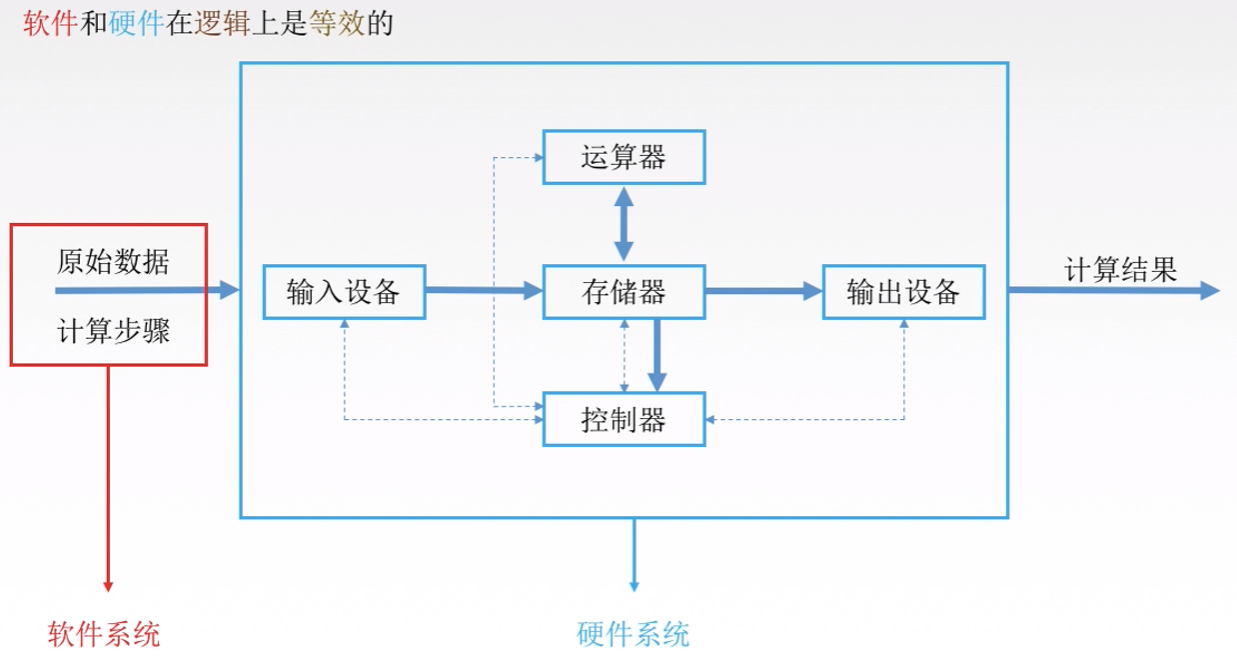

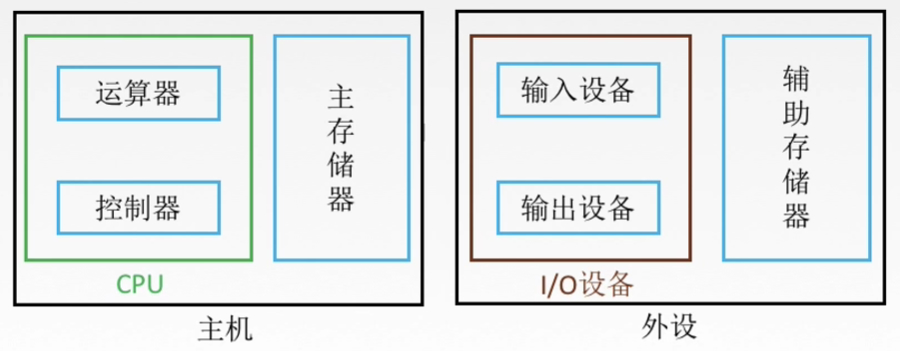

冯诺伊曼体系结构

将程序和数据以机器所能识别和接受的信息形式输入计算机

将计算机处理的结果以人们所能接受的形式或其他系统所要求的信息形式输出

存储器分为主存储器和辅助存储器,cpu能够直接访问的存储器是主存储器

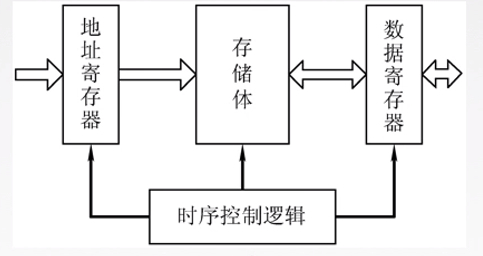

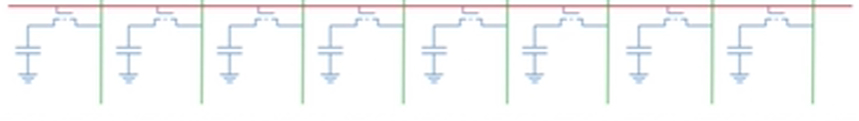

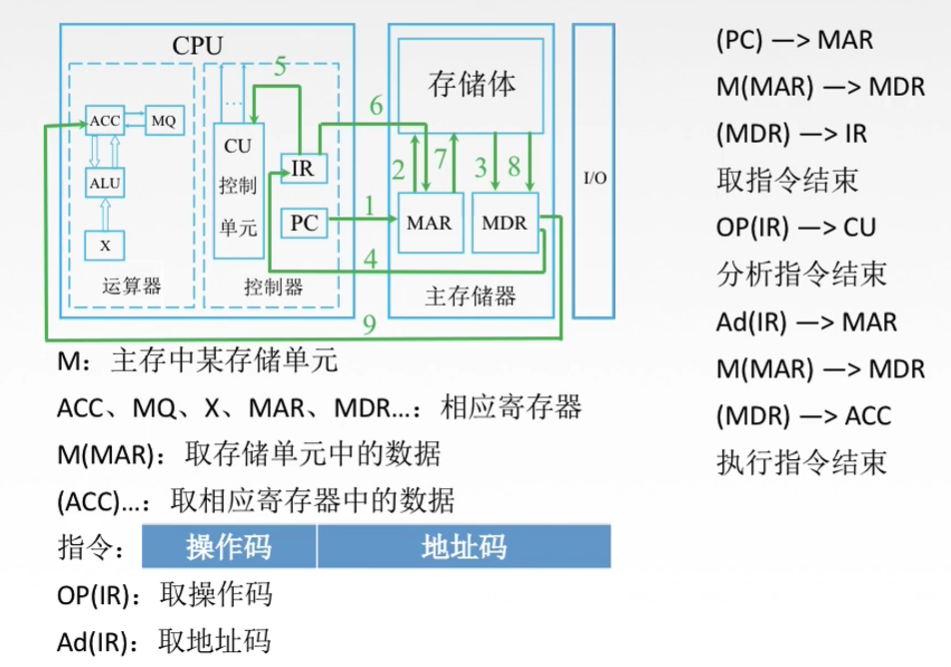

主存储器结构如下

取数时,在地址寄存器中找到数据在存储体中的保存位置,然后将数据放到数据寄存器

全称Memory Address Register,存储的是CPU要访问的内存单元的地址。当CPU需要访问内存中的数据时,它会先将数据在内存中的地址存放在地址寄存器中,然后通过该地址寄存器来读取或写入数据。在执行指令时,CPU会将操作数或操作数的地址存放在地址寄存器中,以方便后续操作

全称Memory Data Register,暂存将要写入到内存的数据或者刚从内存读取出来的数据。数据寄存器可以用来存储CPU从内存中读取的数据、运算结果或中间结果等。CPU在执行指令时,会将需要操作的数据从内存中读取到数据寄存器中,然后在数据寄存器中进行运算或操作。

存储体由多个存储单元组成,每个存储单元包括若干个存储元件,每个存储元件存储一个二进制数据

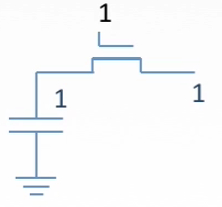

以一个逻辑电路表示一个存储元

多个存储元件构成一个存储单元

存储单元存储的内容为存储字,一般为8bit,一个存储元件存储1bit数据

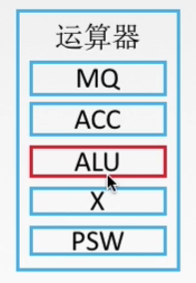

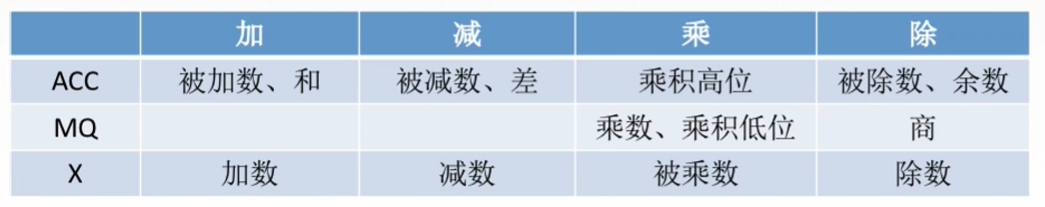

运算器由以下几个部分组成

全称为Arithmetic and Logic Unit,他是计算机中执行算术和逻辑操作的核心组件,用于处理算术运算(如加法、减法、乘法和除法)和逻辑运算(如与、或、非和异或)

全称为Multiple-Quotient Register,在乘除运算时,存放操作数或结果

全称为Accumulator,存储操作数或运算结果

通用寄存器X,存储各种类型的数据,并在运算过程中作为输入和输出操作数

PSW通常包含一些控制信息和状态标志,如中断屏蔽标志、条件码标志、控制方式标志等。在执行程序的过程中,这些标志用于控制程序的流程和决策。

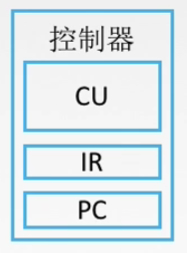

全称为control unit,解释从存储器中取出的指令,并根据指令内容产生相应的控制信号序列,这些信号指导并控制着整个计算机系统的操作流程。CU负责指挥算术逻辑单元(ALU)执行运算、管理数据在存储器与寄存器之间的传输、以及I/O设备的数据交换等操作

全称为instruction register,用于暂存当前正在执行的指令。当从内存中的程序计数器(PC)指定的地址取出一条指令后,该指令会被送入IR中。IR的内容包含了将要被执行的操作码以及可能的操作数地址或立即数信息,通过解码这些信息,控制单元知道该如何执行后续步骤

全称为program counter,存储储下一条待执行指令地址的寄存器。在每个指令周期开始时,PC的内容会被送到内存地址寄存器(MAR),以读取指令;执行完当前指令后,PC通常会自动加1(或其他值,如在分支跳转指令时),从而指向内存中下一条指令的地址,这样保证了程序按照既定顺序或者特定条件转移顺序执行。

CPU由运算器+控制器+主存储器组成

取数流程

(PC) --> MAR:将PC中要操作的指令放到主存中的MAR中。

M(MAR) --> MDR:主存根据MAR中的地址码,找到对应的存储单元,将数据暂存至MDR中

(MDR) --> IR:MDR中存储的指令交给控制器中的IR

此时取指令结束

OP(IR) --> CU:从IR中取出指令里面的操作码,交给CU去解析

此时分析指令已经完成,但是仍然没有拿到要处理的数据

Ad(IR) --> MAR:取出IR中指令的地址码,存储到MAR中

M(MAR) --> MDR:主存更绝MAR中的地址码,找到对应的存储单元,将数据暂存到MDR中

(MDR) --> ACC:将数据从MDR中取出交给ACC

执行指令结束